# International Journal of Scholarly Research in Engineering and Technology

Journal homepage: https://srrjournals.com/ijsret/ ISSN: 2961-3280 (Online)

(RESEARCH ARTICLE)

## Design of two-port SRAM cell with improved write operation

Ming-Hsueh Wu, Chien-Cheng Yu \* and Ming-Chuen Shiau

Department of Electrical Engineering, Hsiuping University of Science and Technology, Taichung 41280, Taiwan.

International Journal of Scholarly Research in Engineering and Technology, 2023, 03(01), 008-015

Publication history: Received on 26 June 2023; revised on 05 August 2023; accepted on 07 August 2023

Article DOI: https://doi.org/10.56781/ijsret.2023.3.1.0045

#### **Abstract**

In this paper, a novel seven-transistor (7T) two-port SRAM cell incorporating an assist circuit is proposed. Wherein, the assist circuit is used to deal with the memory cell failures. During a write operation, this circuit is activated to connect a diode-connected transistor to the source of the drive transistor located near the write bit line. Accordingly, it can provide an efficient solution to the writing '1' issue to improve write operations in this manner. Simulation results for the proposed cell design confirm that there is a conspicuous improvement over the conventional two-port SRAM cells and fast writing also can be achieved.

**Keywords:** Two-port; Assist circuit; Single-ended; Static random access memory; Read-write control circuit

#### 1 Introduction

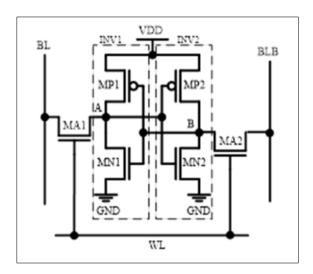

Generally, a memory device is classified into a DRAM (dynamic random access memory) and an SRAM according to its respective data storage capability. DRAM is advantageous for its small size, but requires periodic refreshes to prevent data loss. However, SRAM is advantageous for its simple operations but occupies a large chip area. SRAM circuits are frequently used in most digital integrated circuits to store representations of data bits. SRAM circuits may be single-port or multi-port. In the single-port SRAM, normally, either read and write operation is performed in one access from one port circuit connected to a pair of bit lines to one memory cell. The two-port SRAM, although it can perform a read and a write every clock cycle, requires more circuitry to perform the read and write operations. Figure 1 shows a structure of a conventional six-transistor (6T) single-port SRAM [1]. The cross-coupled structure of inverters INV1 and INV2 ensures that logically opposite voltages are held at storage nodes A and B, respectively.

One drawback of the conventional 6T SRAM cell is that its operation speed and cell size are strictly limited due to reliability concerns. Referring to Fig. 1, the drive transistor MN1 is made larger than the access transistor MA1 as such when both of these two transistors MN1 and MA1 are turned on, the drive transistor MN1 will have a lower resistance than the access transistor MA1. As a result, the drive transistor MN1 will more easily carry current when activated. However, for a successful write operation, it may be necessary that the access transistors should be very conducive to force the latch to change its equilibrium condition. Another drawback is that the data stored in the cells may be corrupted when the cells are read. For example, when a logical '0' is stored initially, the voltage rising in the cell may corrupt the data stored. Consequently, the access transistor should have a reduced conductivity for good stability in reading and standby operations. Therefore, the SRAM cell should provide less likely to be corrupted when the cell is read and more reliable when the cell is written [2]. These requirements impose contradicting requirements on transistor sizing. Recently, the cell ratio of the memory cell is reducing, this problem becomes more critical. One development is a two-port SRAM having dedicated read and write ports that provide high-speed read and write operations in place of the conventional single-port SRAMs [3]-[5].

<sup>\*</sup> Corresponding author: Chien-Cheng Yu

Figure 1 Circuit diagram of the conventional 6T SRAM cell

The remainder of this paper is organized as follows. Section 2 presents a brief description of a conventional 6T and an 8T two-port SRAM cell topologies. The proposed 7T two-port SRAM cell incorporating an assist circuit is described in Section 3. The simulation results of the proposed 7T two-port SRAM cell are discussed in Section 4. The last section is a conclusion and summary of the paper.

### 2 Existing Technologies

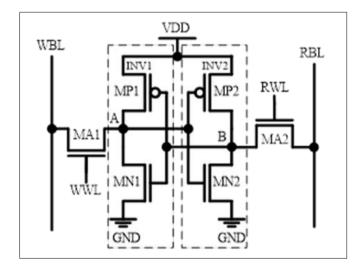

The conventional 6T single-port SRAM cell can be modified to create a two-port SRAM cell. Figure 2 illustrates a conventional 6T two-port SRAM cell, which employs independent word lines (write word line WWL, read word line RWL) and bit lines (write bit line WBL, read bit line RBL) such that the opposite sides of the SRAM cell can be accessible by separate read and write ports [6]. The 6T two-port SRAM memory cell also includes an inverter INV1 mutually cross-coupled to an inverter INV2 to form a latch. The latch of the two-port SRAM itself has the same structure as that of the single-port SRAM, and therefore, the two-port SRAM has the same characteristics for read and write operations as the 6T single-port SRAM. In the write port, the write access transistor MA1 is dedicated exclusively to write operations. Moreover, in the read port, the read access transistor MA2 is devoted exclusively to read operations. In write operations, data is written into the SRAM cell by applying a logic high voltage signal to the write word line WWL, thereby turning the write access transistor MA1 on and coupling node A to the write bit line WBL. Alternately, data is read from the cell by applying a logic high voltage signal to the read word line RWL, thereby turning the read access transistor MA2 on and coupling node B to the read bit line RBL.

Figure 2 Circuit diagram of the conventional 6T two-port SRAM cell

Although the 6T two-port SRAM cell can be processed in the same manner as a conventional 6T single-port SRAM cell in write operations, a concern associated with the write operation is that it is relatively difficult to write a logical '1' to the cell if the cell currently stores a logical '0'. The difficulty with write operations lies in the fact that it is very difficult to write a logical '1' into the storage node A using only a single-ended write bit line structure [7]-[8]. To provide full two-port memory functionality, several techniques have been developed [9]-[14]. These techniques usually increase or decrease a voltage applied to an individual memory cell. For example, boosting the voltage on a word line during a write cycle can improve the write margin of an SRAM memory cell. Lowering the voltage on a bit line below ground voltage during a write cycle can also improve the ability to write to a memory cell.

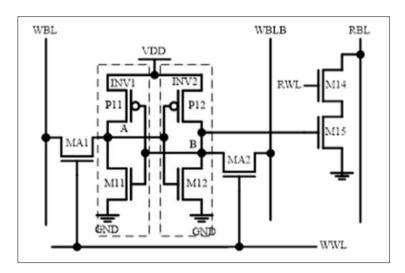

The conventional 6T single-port SRAM cell can also be made into an 8T two-port cell by inserting two additional transistors into the SRAM cell that implement a separate read port connected to a corresponding read bit line RBL and read word line RWL, as shown in Fig. 3 [9], [15]. The read port further comprises a read access transistor M14 and a read drive transistor M15 coupled in series to become a read stack. The reading of the data stored in the SRAM cell is performed through the read access transistor M14 and the read drive transistor M15. The storage node A is coupled to the write bit line WBL through the write access transistor MA1, while the storage node B is coupled to the write bit line WBLB through the write access transistor MA2, wherein the storage nodes A and B are complementary nodes that are often at opposite voltage levels.

Before a write operation is performed, the write word line WWL is asserted. In write operations, the read access transistor M14 is turned off, and the write access transistors MA1 and MA2 are turned on. Accordingly, the data value is written into the cell through the write bit lines WBL and WBLB. Finally, at the end of the write operation, the write word line WWL is de-asserted, allowing the latch to function normally and hold the data of the storage node. It's worth noting that, to guarantee a successful write operation, the storage node A must be pulled up (or down) above (or below) the trip-voltage of the inverter INV2 during the write word line WWL is asserted, otherwise a write failure will occur. Instead, when a read operation is performed, the read bit line RBL is pre-charged during the read operation. Meanwhile, the write access transistors MA1 and MA2 are turned off, and the read access transistor M14 is turned on. If the storage node A is charged to a logic high, the read drive transistor M15 will be turned on and the voltage on the read bit line RBL will be pulled down to the ground. On the contrary, if the storage node A is discharged to a logic low, the read drive transistor M15 will be turned off and the voltage on the read bit line RBL will remain at its pre-charged level. Then, the sensing current on the read bit line RBL is detected by a sense amplifier (not shown) to determine the logic state of the cell.

Figure 3 Circuit diagram of the conventional 8T two-port SRAM cell

Advantageously, using the read-port of the 8T SRAM cell, the gate of the read drive transistor M15 receives the storage node voltage directly. Therefore, the data stored in the storage node B is not affected during the read operation through the read port. Particularly, the read operation based on this read port has a characteristic in that this operation can be carried out completely independent of the write port, without destroying the data of the storage nodes A and B of the cell. However, the conventional 8T two-port SRAM cell has a large cell size due to eight transistors in total. As such, it is desirable to provide an SRAM cell that has the two-port functionality while maintaining a relatively small cell size.

#### 3 Proposed Technology

Recently, several techniques have been developed to resolve the write '1' issue of the SRAM cells configured with a single-ended write bit line. Some of these techniques rely on boosted word line voltage [16]-[18], reducing the supply voltage VDD [19]-[21], sizing cell transistors [22]-[23], and raising the source voltage VSS [24]-[25]. However, each of these techniques may cause a reduction in the drive current of the transistors and in the operating speed of the cell or may increase memory cell area. Other techniques require the generation of a voltage above the operating voltage or require a more complicated circuit design and a more complicated device process. Therefore, there is a need for an effective technique to improve the write operation of the SRAM cells configured with single-ended write bit lines, which suffer from an inability to write '1'.

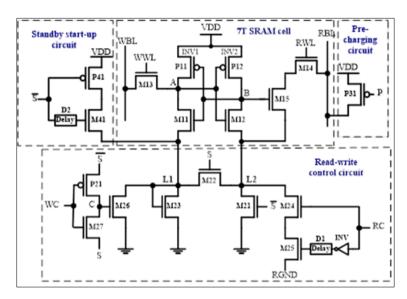

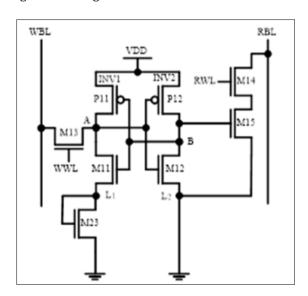

Figure 4 Circuit diagram of the proposed 7T SRAM cell

#### 3.1 The Proposed 7T Two-Port SRAM Cell Structure

The proposed 7T two-port SRAM cell structure includes a write port and a read port as shown in Fig. 4. The write port is configured to connect the latch, similar to that of the above-mentioned cells, to the write bit line WBL in response to a write signal on the write word line WWL for writing a logical state to the memory cell. The gate of the transistor M13 is connected to a corresponding write word line WWL for conveying a write signal. The memory cell further comprises a read port configured to read the logic state of the latch in response to a read signal on the read word line RWL. The read port of the cell includes a pair of series-connected NMOS transistors M14 and M15, wherein the gate of transistor M14 is connected to the read word line RWL and the gate of transistor M15 is coupled to the storage node B.

It's worth noting that transistors P11 through P12 and M11 through M15 are appropriately sized to make the read and write states perform properly. Furthermore, the proposed cell structure also incorporates an assist circuit which consists of a read-write control circuit, a pre-charging circuit, and a standby start-up circuit. Still referring to Fig. 4, the read-write control circuit is coupled to the source terminals corresponding to the drive transistors of each row of memory cells. This configuration is aimed to control the source voltages of the drive transistors under different operating modes. That is, the read-write control circuit is configured to control the voltage levels of the nodes L1 and L2 (VL1 and VL2, hereafter) in response to different operating modes. For example, during a read mode or during a standby mode, the read-write control circuit is configured to connect the voltage levels of the nodes L1 and L2 of the selected cell to the ground. Further, during a write operation, the read-write control circuit is configured to provide the voltage of the node L1 with an NMOS threshold voltage, and the voltage of the node L2 with a ground voltage. In addition, the pre-charging circuit is connected to the read bit line RBL in each column. The function of the pre-charging circuit is to pull up the read bit line RBL of a selected column to VDD before the read operation. Furthermore, the standby start-up circuit is to enable the SRAM cell to quickly switch to the standby mode, and thus effectively enhance the standby performance. In this manner, the memory cell has the advantage of having little or no adverse impact on cell stability or the write margin along with a relatively small cell size compared to the conventional two-port SRAM cells.

#### 3.2 Write Operation

Referring again to Fig. 4, prior to the write operation being performed, the write control signal WC is at logic low, the transistor P21 is turned on and the transistor M27 is turned off. Thereby, the node C is at logic high, and thus to turn on the transistor M26, the voltage VL1 is pulled down to the ground voltage. However, during the write operation, the signal WC is at logic high, the transistor P21 is turned off and the transistor M27 is turned on. Subsequently, node C is at logic low, and thus to turn off the transistor M26, the voltage VL1 is set to VGS(M23). Thus, the writing '1' issue can be resolved. Figure 5 shows the simplified circuit diagram during the write operation.

Referring to Fig. 5, before a write operation is performed, the write bit line WBL is pre-charged to a logic high. The logic state on the write bit line WBL can be inversed depending on the value to be written into the cell. And, the write word line WWL is then asserted to turn on the access transistor M13 allowing the data to be stored in the cell. When writing a logical '1', the write access transistor M13 and the drive transistor M11 together act as a voltage divider. As such, the node A will be charged toward the following voltage level:

where RM11, RM13 and RM23 are the on-resistance of transistors M11, M13 and M23, respectively. At this moment, the transistor M13 is still in the saturation region, and transistor M11 is in the triode region. Although RM13 may be greater than RM11, the NMOS diode transistor M23 can provide a voltage VGS (M23) (i.e., the gate-source voltage of the transistor M23) at node L1. Consequently, to prevent the writing '1' issue during a write operation, the voltage VL1 of the selected cell is set to a predetermined voltage VGS(M23) which is higher than the ground voltage. Also, the voltage VL2 of the selected cell is set to the ground voltage.

Figure 5 The simplified circuit diagram during the write operation

#### 4 Simulation and Results

To evaluate performance, different SRAM cell structures discussed in this paper were simulated using a 0.18 um CMOS technology. All simulations were carried out at nominal conditions: VDD=1.8 V and at room temperature.

The transients associated with a writing operation are detailed and described below. Firstly, consider the write '0' operation. Prior to the write '0' operation, the write word line WWL is at logic low. During the write '0' operation, if a logical '0' is stored previously, the write word line WWL transitions from a logic low to a logic high. As the voltage level of the write word line WWL (VWWL) exceeds the threshold voltage of the transistor M13 (VTM13), transistor M13 is turned on. Subsequently, owing to the fact that the voltage level of the write bit line WBL (VWBL) is at logic low, the voltage VA remains at the ground voltage. On the other hand, if a logical '1' is stored previously, when the write word line WWL transitions from a logic low to a logic high during the write '0' operation. As the voltage level of the write word line WWL (VWWL) exceeds the threshold voltage VTM13, transistor M13 is turned on. Subsequently, owing to the

fact that the voltage level of the write bit line WBL (VWBL) is at logic low, node A and node L1 will be discharged to the ground until the end of the write '0' operation.

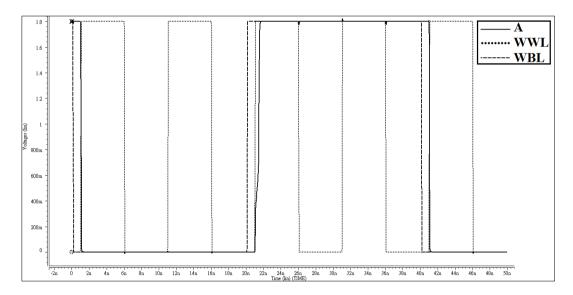

Secondly, consider the write '1' operation. Prior to the write '1' operation, the write word line WWL is at logic low. During the write '1' operation, if a logical '1' is stored previously, the write word line WWL transitions from a logic low to a logic high. As the voltage VWWL exceeds the threshold voltage VTM13, transistor M13 is turned on. Subsequently, owing to the fact that the voltage VWBL is at logic high and transistor P11 is still on, the voltage VA remains at the power supply voltage VDD. On the other hand, if a logical '0' is stored previously, the write word line WWL is at logic low and transistor M11 is turned on. It is to be noted that, since the transistor M11 is turned on, and therefore, when the write '1' operation is started, the write word line WWL transitions from a logic low to a logic high. The voltage at node A is slightly increased following the voltage of the write word line WWL due to the parasitic capacitance coupling effect. As the voltage VWWL exceeds the threshold voltage VTM13, transistor M13 is turned on. Subsequently, since the voltage VWBL is at logic high and transistor M11 is still on, and the voltage VB remains at a voltage close to the power supply voltage VDD, therefore, transistor P11 remains off. As a result, the voltage at node A will rise up due to the voltage division along the drive and access transistors. When the voltage exceeds a threshold, it causes the bit to flip due to regenerative feedback. Hence, the write '1' operation is completed. It is worth noting that, when writing a logical '1' to a logical '0' is stored previously, the voltage VL1 is set to VGS(M23). After completing the write '1' operation, the voltage VL1 will be discharged to the ground voltage via transistor M26. Thus, the issue concerning the difficulty of writing '1' can be resolved. The simulated waveform of successful writing in the proposed 7T SRAM cell is shown in Fig. 6. Table 1 illustrates a comparison among different supply voltages for the traditional 6T SRAM cell and the proposed 7T SRAM cell are performed in a write operation. As can be seen from Table 1, the proposed 7T SRAM cell provides an efficient solution to the writing '1' issue, that is, the proposed 7T SRAM cell enables a logical '1' to be easily written to the SRAM cell, as compared to the standard 6T SRAM cell.

Figure 6 Transient waveforms of a successful writing in the proposed 7T SRAM cell

**Table 1** Write Time of writing a logical '1' comparison

| Power supply voltage (V) | Standard 6T SRAM (ns) | Proposed 7T SRAM (ns) | Improvement (%) |

|--------------------------|-----------------------|-----------------------|-----------------|

| 1.75                     | 0.7688747             | 0.7110508             | 7.5             |

| 1.70                     | 0.256847              | 0.2547118             | 0.83            |

| 1.65                     | 4.360183              | 4.358231              | 0.0448          |

#### 5 Conclusion

This paper has addressed the disadvantages of the existing two-port SRAM cells and further drawbacks inherent to single-ended bit line cells and has provided an assist circuit for resolving the writing '1' issue. This assist circuit is activated to control the source voltages of the drive transistors in a different operating mode. In particular, in a write

operation, the source terminal of the drive transistor located near the write bit line is set to a positive threshold voltage. Meanwhile, the other drive transistor has its source terminal coupled to the ground. Using this method, this design facilitates efficient writing of data into a single-ended write structure in an SRAM cell, particularly if a logical '0' stored in the cell is to be overwritten by a logical '1'. Simulation results for the proposed cell design confirm that the proposed cell provides an efficient solution to the writing '1' issue, that is, the proposed 7T SRAM cell enables a logical '1' to be easily written to the SRAM cell. In addition, the proposed cell design also has the advantage of faster write operations without reducing cell stability.

#### Compliance with ethical standards

Disclosure of conflict of interest

No conflict of interest to disclosed.

#### References

- [1] J. Rabaey, A. Chandrakasan, and B. Nikolic, Digital Integrated Circuits: A Designer Perspective, 2nd ed., Upper Saddle River, NJ: Prentice-Hall, 2003.

- [2] K. Itoh, VLSI Memory Chip Designs, Heidelberg, Springer-Verlag, 2001.

- [3] H. Tran, "Demonstration of 5T SRAM and 6T Dual-Port RAM Cell Arrays," in Proc. 1996 Symp. VLSI Circuits Dig. Tech. Papers, 1996, pp. 68-69.

- [4] Y. Luthra, "Dual port SRAM with dedicated read and write ports for high speed read operation and low leakage," U.S. Pat. 7813161, Oct. 12, 2010.

- [5] K. Nii, et al., "Synchronous Ultra-High-Density 2RW Dual-Port 8T-SRAM with Circumvention of Simultaneous Common-Row-Access," IEEE J. Solid-State Circuits, vol. 44, no. 3, pp. 977-986, Mar. 2009.

- [6] B. Wang and J. B. Kuo, "A novel two-port 6T CMOS SRAM cell structure for low-voltage VLSI SRAM with single-bit-line simultaneous read-and-write access (SBLSRWA) capability," In Proc. 2000 IEEE Int. Symp. Circuits Syst., 2000, pp. 733-736.

- [7] C. C. Wang, C. H. Liao, and S. Y. Chen, "A single-ended disturb-free 5T loadless SRAM with leakage sensor and read delay compensation using 40 nm process," In Proc. 2014 IEEE Int. Symp. Circuits and Systems (ISCAS), 2014, pp.1126-1129.

- [8] J. J. Liaw, "SRAM cell with separate read and write ports," U.S. Pat. 7660149, Feb. 9, 2010.

- [9] J. J. Liaw, "Two-port 8T SRAM design," U.S. Pat. 8144540, Mar. 27, 2012.

- [10] C. C. Yu and M. C. Shiau. "Single-Port 5T SRAM Cell with Improved Write-Ability and Reduced Standby Leakage Current," Int. J. Information and Electronics Engineering, vol. 7, no. 1, pp. 22-28, Jan. 2017.

- [11] V. Rukkumani and N. Devarajan,"Design and Analysis of 8T/10T SRAM cell using Charge Recycling Logic," Int. J. Computer Science Engineering (IJCSE), vol. 4, no. 4, pp. 166-172, July 2015.

- [12] Y. W. Chiu, et al.,"40 nm Bit-Interleaving 12T Subthreshold SRAM with Data-Aware Write-Assist," IEEE Trans. Circuits and Systems, vol. 61, no. 9, pp. 2578-2585, Sept. 2014.

- [13] R. Hobson, "A New Single-Ended SRAM Cell With Write-Assist," IEEE Trans. Very Large Scale Integration (VLSI) Systems, vol. 15, no. 2, pp. 173-181, Feb. 2007.

- [14] T. Suzuki, et al., "A Stable 2-Port SRAM Cell Design Against Simultaneously Read/Write-Disturbed Accesses," IEEE J. Solid-State Circuits, vol. 43, no. 9, pp. 2109-2119, Sep. 2008.

- [15] S. Ishikura, et al., "A 45 nm 2-port 8T-SRAM Using Hierarchical Replica Bitline Technique With Immunity From Simultaneous R/W Access Issues," IEEE J. Solid-State Circuits, vol. 43, no. 4, pp. 938-945, Apr. 2008.

- [16] N. Verma and A. P. Chandrakasan, "A 256 kb 65nm 8T subthreshold SRAM employing sense-amplifier redundancy," IEEE J. Solid-State Circuits, vol. 43, no. 1, pp. 141-149, 2008.

- [17] S. Nalam, et al., "Asymmetric 6T SRAM with two-phase write and split bit line differential sensing for low voltage operation," in Proc. 11th Int. Symp. Quality Electronic Design (ISQED), Mar. 2010, pp. 139-146.

- [18] Y. H. Chen, et al., "A 0.6V 45nm adaptive dual-rail SRAM compiler circuit design for lower VDD\_min VLSIs," in Proc. IEEE Symp. VLSI Circuits, June 2008, pp. 210-211.

- [19] Y. Chung and S. H. Song, "Implementation of low-voltage static RAM with enhance data stability and circuit speed," Microelectronics Journal, vol. 40, no. 6, pp. 944-951, 2009.

- [20] M. Yamaoka, et al., "Low-power embedded SRAM modules with expanded margins for writing," in Proc. IEEE Int. Conf. Solid-State Circuits (ISSCC 2005), Feb. 2005, pp. 480-611.

- [21] H. Pilo, et al., "An SRAM design in 65nm and 45nm technology nodes featuring read and write-assist circuits to expand operating voltage," in IEEE Symp. VLSI Circuits, 2006, pp. 15-16.

- [22] D. P. Wang, et al., "A 45nm dual-port SRAM with write and read capability enhancement at low voltage," in Proc. IEEE Int. SOC Conf., Sept. 2007, pp. 211-214.

- [23] K. J. O'Connor, "A source sensing technique applied to SRAM cells," IEEE J. Solid State Circuits, vol. 30, no. 4, pp. 500-511, Apr. 1995.

- [24] M. H. Tu, et al., "Single-Ended Subthreshold SRAM with Asymmetrical Write/Read-Assist," IEEE Trans. Circuits and Systems- I: Regular Papers, vol. 57, no. 12, pp. 3039- 3047, Dec. 2010.

- [25] K. Kim, J. J. Kim, and C. T. Chuang, "Asymmetrical SRAM cells with enhanced read and write margins," in Proc. Int. Symp. VLSI Technology, Systems and Applications (VLSI-TSA), Apr. 2007, pp.1-2.